# Institut für Mikroelektronik Stuttgart

A complete list of all semiconductor processes available at the IMS

Institut für Mikroelektronik Stuttgart Foundation under civil law

**IMS CHIPS**

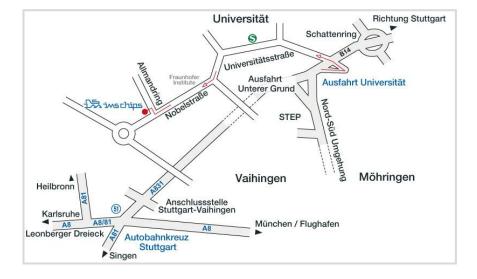

Allmandring 30a 70569 Stuttgart

Phone+49 711 21855-0 Fax +49 711 21855-111 Email info@ims-chips.de

http://www.ims-chips.de

# Institut für Mikroelektronik Stuttgart

The IMS develops and manufactures electronic and mechanical semiconductor components, MEMS, replication masters, (diffractive) optical elements, ultra-thin chips, photonic systems, GaN devices and that in addition to many more products in its clean rooms. To outline these tasks, there is an extensive portfolio of available semiconductor processes at the IMS.

Our range of performance

- Qualified individual processes and process chains for silicon and quartz wafers up to 200 mm, in individual cases even up to 300 mm

- Qualified single processes and process chains for 6" and 9" standard quartz masks as well as for round 12" and 17" optical substrates

- Extensive portfolio of lithographic processes including i-Line stepper, laser direct writing, e-beam direct writing, and back and proximity lithography

- Packaging technology and advanced packaging processes

- IECQ und ISO 9001 certification

Our infrastructure

- 1,400 m<sup>2</sup> ISO04 clean room

- Comprehensive wafer processing line

- Manufacturing line for 6" and 9" standard quartz masks as well as for round 12" and 17" optical substrates

- Packaging and interconnection technology with wafer processing up to 200 mm incl. back thinning

- Comprehensive testing and quality assurance environment

The IMS offers the listed individual or processing cycles as well as measurement services in combination with technical consulting for research & development where required or the support of manufacturing lines as a service.

Partnering with our customers we also develop new processes or technologies based on our equipment.

## Content

| 1                                                                                       | Late       | ral furnace processing                                                         | 5      |  |

|-----------------------------------------------------------------------------------------|------------|--------------------------------------------------------------------------------|--------|--|

|                                                                                         | 1.1        | Oxidation                                                                      |        |  |

|                                                                                         | 1.2        | Diffusion                                                                      |        |  |

|                                                                                         | 1.3        | POCI <sub>3</sub> coating                                                      | 5      |  |

| 2                                                                                       | Laye       | er deposition                                                                  | 5      |  |

|                                                                                         | 2.1        | Silicon oxide deposition                                                       | 5      |  |

|                                                                                         | 2.2        | Silicon nitride deposition:                                                    |        |  |

|                                                                                         | 2.3        | Polysilicon deposition:                                                        |        |  |

|                                                                                         | 2.4<br>2.5 | Aluminum sputtering                                                            |        |  |

|                                                                                         | 2.5        | Titanium sputtering<br>Titanium nitride sputtering                             |        |  |

|                                                                                         | 2.7        | Chromium sputtering                                                            |        |  |

|                                                                                         | 2.8        | Metal vaporization                                                             |        |  |

| 3                                                                                       | Litho      | ography                                                                        | 7      |  |

| 0                                                                                       | 3.1        | Coating and development of photo resists on wafers                             |        |  |

|                                                                                         | 3.2        | Coating and development of photo resists on waters                             |        |  |

|                                                                                         | 3.3        | Contact exposure                                                               |        |  |

|                                                                                         | 3.4        | Step and repeat exposure                                                       |        |  |

|                                                                                         | 3.5        | Laser direct writing                                                           |        |  |

|                                                                                         | 3.6        | E-beam exposure                                                                | 7      |  |

| 4                                                                                       | Dry        | chemical etching of wafers                                                     | 8      |  |

|                                                                                         | 4.1        | Silicon oxide etching                                                          | 8      |  |

|                                                                                         | 4.2        | Silicon nitride etching                                                        |        |  |

|                                                                                         | 4.3        | Poly silicon etching                                                           |        |  |

|                                                                                         | 4.4<br>4.5 | High-rate silicon etching                                                      |        |  |

|                                                                                         | 4.6        | Titanium/titanium nitride etching                                              |        |  |

|                                                                                         | 4.7        | Isotropic dry etching                                                          |        |  |

| 5                                                                                       | Dry        | chemical etching of quartz wafers and photo mask substrates                    | 9      |  |

|                                                                                         |            | mical mechanical polishing                                                     |        |  |

|                                                                                         |            |                                                                                |        |  |

| 7                                                                                       |            | er marking                                                                     |        |  |

| 8                                                                                       | Cha        | racterization of layers and structures on silicon wafers and mask substrates   |        |  |

|                                                                                         | 8.1        | Layer thickness measurement with white light interferometry                    |        |  |

|                                                                                         | 8.2        | Measurement of layer thickness and refraction index with spectral ellipsometry |        |  |

|                                                                                         | 8.3<br>8.4 | Measurement of height profiles<br>Measurement of precise location              | 9<br>0 |  |

|                                                                                         | 8.5        | Measurement of structures on wafers and mask substrates with scanning electron | 5      |  |

|                                                                                         |            | scopy                                                                          | 0      |  |

| 8.6 Characterization of structures on wafers and mask substrates with scanning electron |            |                                                                                |        |  |

|                                                                                         |            | scopy                                                                          |        |  |

|                                                                                         | 8.7        | Characterization of thin dielectric layers on wafers                           |        |  |

|                                                                                         | 8.8        | Defect measurement (Light Point Defects, LPD) on wafers1                       | U      |  |

|      | Measurement of structures, height profiles, and surface roughness using atomic fore scopy (AFM) |                                                                                                                                                                                                                                                                                                                                                                       |

|------|-------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pac  | kaging                                                                                          | . 11                                                                                                                                                                                                                                                                                                                                                                  |

| 9.1  | Wafer thinning                                                                                  | . 11                                                                                                                                                                                                                                                                                                                                                                  |

| 9.2  | Sawing silicon wafers                                                                           |                                                                                                                                                                                                                                                                                                                                                                       |

| 9.3  | Removing dies from foil                                                                         | . 11                                                                                                                                                                                                                                                                                                                                                                  |

| 9.4  | Die bonding                                                                                     | . 11                                                                                                                                                                                                                                                                                                                                                                  |

| 9.5  | Wire bonding                                                                                    | . 11                                                                                                                                                                                                                                                                                                                                                                  |

| 9.6  |                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                       |

| 9.7  | Baking oven                                                                                     | . 11                                                                                                                                                                                                                                                                                                                                                                  |

| 9.8  | Package seal                                                                                    | . 12                                                                                                                                                                                                                                                                                                                                                                  |

| 9.9  | Packaging or solder cleaning                                                                    | . 12                                                                                                                                                                                                                                                                                                                                                                  |

| 9.10 |                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                       |

| 9.11 | Package printing                                                                                |                                                                                                                                                                                                                                                                                                                                                                       |

|      |                                                                                                 | nicroscopy (AFM)<br>Packaging<br>9.1 Wafer thinning<br>9.2 Sawing silicon wafers<br>9.3 Removing dies from foil<br>9.4 Die bonding<br>9.5 Wire bonding<br>9.5 Wire bonding<br>9.6 Testing of the wire/bonding and soldering connections<br>9.7 Baking oven<br>9.8 Package seal<br>9.9 Packaging or solder cleaning<br>9.10 Testing the impermeability of the packages |

Contact

Dr. Martin Zimmermann Dr. Jörg Butschke phone: +49 711 21855-423 phone: +49 711 21855-453

## 1 Lateral furnace processing

### 1.1 Oxidation

Manufacture of oxide layers with thicknesses between 7 nm and 3  $\mu$ m on 100 mm, 150 mm and 200 mm silicon wafers; oxidation is carried out in a horizontal Centrotherm E1550 furnace.

### 1.2 Diffusion

Annealing of implantation damage and activation of dopands in 100 mm, 150 mm and 200 mm silicon wafers in a nitrogen or in an oxidizing atmosphere; diffusion is carried out in a horizontal Centrotherm E1550 furnace.

### **1.3 POCI<sub>3</sub> coating**

Phosphor doping of mono-crystalline and polycrystalline silicon by creating a phosphor glass on 100 mm, 150 mm and 200 mm silicon wafers, configuration is carried out in a horizontal Centrotherm E1550 furnace.

## 2 Layer deposition

## 2.1 Silicon oxide deposition

PECVD (Plasma Enhanced Chemical Vapour Deposition): Deposition of silicon oxide layers (silane-based) with thicknesses between 300 nm and 2  $\mu$ m on 150 mm silicon wafers; deposition is carried out in an Applied Materials Centura (DxZ-Chamber).

TEOS LPCVD (Low Pressure Chemical Vapour Deposition): Deposition of silicon oxide layers with thicknesses between 50 nm and 500 nm on 150 mm and 200 mm silicon wafers; deposition is carried out in a horizontal Centrotherm E1550 furnace.

TEOS PECVD (Plasma Enhanced Chemical Vapour Deposition): Deposition of silicon oxide layers with thicknesses between 50 nm and 5  $\mu$ m on 150 mm silicon wafers; deposition is carried out in an Applied Materials Centura (DxZ-Chamber).

SACVD (Sub Atmospheric Chemical Vapour Deposition): Deposition of undoped silicon oxide layers (USG) with thicknesses between 50 nm and 1.5  $\mu$ m on 150 mm silicon wafers; deposition is carried out in an Applied Materials Centura (CxZ-Chamber).

## 2.2 Silicon nitride deposition:

LPCVD (Low Pressure Chemical Vapour Deposition): Deposition of silicon nitride layers with thicknesses between 50 nm and 500 nm on 150 mm and 200 mm silicon wafers; deposition is carried out in a horizontal Centrotherm E1550 furnace.

PECVD (Plasma Enhanced Chemical Vapour Deposition): Deposition of silicon oxide layers with thicknesses between 300 nm and 2  $\mu$ m on 150 mm silicon wafers; deposition is carried out in an Applied Materials Centura (DXz-Chamber).

## 2.3 Polysilicon deposition:

LPCVD (Low Pressure Chemical Vapour Deposition): Deposition of undoped polysilicon layers with thicknesses between 70 nm and 1000 nm on 150 mm and 200 mm silicon wafers; deposition is carried out in a horizontal Centrotherm E1550 furnace.

## 2.4 Aluminum sputtering

Sputtering (Physical Vapour Deposition, PVD) on AISi layers with thicknesses between 100 nm and 4  $\mu$ m on 150 mm wafers; deposition is carried out in an Applied Materials Endura; layer composition = AISi(1%).

Sputtering (Physical Vapour Deposition, PVD) of super-pure aluminum layers with thicknesses between 50 nm and 2 nm on 100 mm, 150 mm and 200 mm as well as samples in various sizes up to a 200 mm diameter; deposition is carried out in a Leybold Z590.

## 2.5 Titanium sputtering

Sputtering (Physical Vapour Deposition, PVD) of titanium layers with thicknesses between 15 nm and 100  $\mu$ m on 150 mm wafers; deposition is carried out in an Applied Materials Endura.

Sputtering (Physical Vapour Deposition, PVD) of titanium layers with thicknesses between 20 nm and 200 nm on 100 mm, 150 mm and 200 mm as well as samples in various sizes up to a 200 mm diameter; deposition is carried out in a Leybold Z590.

## 2.6 Titanium nitride sputtering

Reactive sputtering (Physical Vapour Deposition, PVD) of titanium nitride layers with thicknesses between 25 nm and 100 nm on 150 mm wafers; deposition is carried out in an Applied Materials Endura.

## 2.7 Chromium sputtering

Sputtering (Physical Vapour Deposition, PVD) of chromium layers with thicknesses between 20 nm and 200 nm on 100 mm, 150 mm and 200 mm as well as samples in various sizes up to a 200 mm diameter; deposition is carried out in a Leybold Z590.

## 2.8 Metal vaporization

Vaporization of aluminum/molybdenum/nickel and titanium layers with thicknesses of 5 nm up to 1  $\mu$ m on 150 mm and 200mm wafers. Deposition is carried out with a type Leybold UNIVEX 900 vaporization equipment by the Leybold company. Vaporization of chromium, nickel, aluminum and gold layers with thicknesses of 10 nm up to 1  $\mu$ m on 100 mm, 150 mm und 200 mm wafers. Deposition is carried out with a type Leybold 500 vaporization equipment by the Leybold company.

## 3 Lithography

## 3.1 Coating and development of photo resists on wafers

Coating and spray coating, development with alcaline-aqueous and solvent media on 150 mm, 200 mm and 300 mm wafers; processing is carried out with a Süss MicroTech Gamma or an Osiris VARIXX1204.

## 3.2 Coating and development of photo resists on photo masks

Coating and development with alcaline-aqueous and solvent media on 6 inch and 9 inch mask substrates; processing is carried out with a EVG150, EVG101 and a Süss MicroTech Delta.

## 3.3 Contact exposure

Contact exposure and proximity exposure of photo-sensitive layers on 150 mm wafers and 6" mask substrates with a minimal lateral resolution in the sub  $\mu$ m range; exposure is carried out with a EVG 6200NT contact exposer.

## 3.4 Step and repeat exposure

Exposure of photo-sensitive layers using the step and repeat process on 150 mm wafers with a minimal lateral resolution of 350 nm; exposure is carried out with a Canon FPA 3030 i5a Stepper.

## 3.5 Laser direct writing

Exposure of photo coating with a laser direct writer (VPG400 made by Heidelberg Instruments) with a minimal resolution of 0.7  $\mu$ m on variable substrate sizes with an edge length of 400 mm and a maximum thickness of 9 mm. Automatic handling of 150 mm wafers and 6" mask substrates.

Exposure of photo coating with a laser direct writer HIMT ULTRA made by Heidelberg Instruments with a minimal resolution of  $0.4\mu m$  on 6" and 9" mask substrates and 150 mm and 200 mm wafers. Max. writing area is 210 mm x 210 mm

## 3.6 E-beam exposure

Exposure of photo coating with a Variable Shaped Beam writer on 150 mm or 300 mm wafers as well as right-angled 6 inch or 9 inch quartz substrates (6025 or 9035 masking blanks) with a minimal resolution of 50 nm grid structures; exposure is carried out with a throughput efficient VSB writers Vistec SB4050SA or SB255.

Contact

Dr. Martin Zimmermann Dr. Jörg Butschke phone: +49 711 21855-423 phone: +49 711 21855-453

## 4 Dry chemical etching of wafers

## 4.1 Silicon oxide etching

Anisotropic dry etching of silicon oxide layers with thicknesses of up to 5  $\mu$ m on 150 mm wafers with Reactive Ion Etching (RIE) processes; etching is carried out in an Applied Materials Etch-Centura with an eMxP+ chamber.

## 4.2 Silicon nitride etching

Anisotropic dry etching of silicon nitride layers with thicknesses of up to 3  $\mu$ m on 150 mm wafers with Reactive Ion Etching (RIE) processes; etching is carried out in an Applied Materials Etch-Centura with an eMxP+ chamber.

## 4.3 Poly silicon etching

Anisotropic dry etching of mono and poly silicon layers with thicknesses of up to 2  $\mu$ m on 150 mm wafers with Reactive Ion Etching (RIE) processes; etching is carried out in an Applied Materials Etch-Centura with an eMxP+ chamber combining a high degree of selectivity to silicon oxide stop layers.

## 4.4 High-rate silicon etching

High-rate dry etching of silicon on 150 mm and 200 mm wafers with the Bosch process (Deep Reactive Ion-Etching, DRIE), structural sizes possible from sub 100 nm structures to several 100  $\mu$ m, feasible aspect ratios of 50:1; etching is carried out in a STS Pegasus.

## 4.5 Aluminum etching

Anisotropic dry etching of aluminum layers with thicknesses of up to  $5 \,\mu$ m on 150 mm wafers with Reactive Ion Etching (RIE) processes; etching is carried out in a LAM Rainbow.

## 4.6 Titanium/titanium nitride etching

Anisotropic dry etching of titanium and titanium nitride layers with thicknesses of up to 200 nm on 150 mm wafers with Reactive Ion Etching (RIE) processes; etching is carried out in a LAM Rainbow.

## 4.7 Isotropic dry etching

Isotropic etching of burried dielectric layers and dielectric mask layers on 150 mm and 200 mm silicon wafers with nearly endlessly high selectivity to all common CMOS metals; etching is carried out in a Primaxx HF etcher.

Isotropic etching of poly silicon, silicon oxide and silicon nitride on 150 mm silicon wafers with high selectivity to all common CMOS metals; etching is carried out in a Matrix 303 etching equipment.

## 5 Dry chemical etching of quartz wafers and photo mask substrates

Anistropic dry etching of Cr or TaN/TaBN layers with thicknesses of up to 300 nm on 150 mm quartz substrates or 6 inch and 9 inch photo mask substrates with a  $Cl_2$ - $O_2$  chemistry; etching is carried out in a PlasmaTherm ICP etcher.

Anistropic dry etching of quartz or MoSi layers on 150 mm quartz substrates or 6 inch and 9 inch photo mask substrates with fluorine processing; etching is carried out in a PlamaTherm ICP etcher.

## 6 Chemical mechanical polishing

Planarization and thinning of silicon and poly silicon on 100 mm and 150 mm wafers, leveling depending on structural size and density; planarization is carried out in an Alpsitec Mecapol 460 CMP.

## 7 Wafer marking

Fully automatic and particle-free marking of 150 mm und 200 mm wafers, free selection of font and location possible; marking is carried out with a fully automatic Innolas 2000DPS laser marker.

## 8 Characterization of layers and structures on silicon wafers and mask substrates

### 8.1 Layer thickness measurement with white light interferometry

Measurement of thin layers made of silicon oxide, silicon nitride, poly silicon and photo resist on 150 mm silicon wafers with layer thicknesses of 50 nm up to several hundred micrometers; measurement is carried out with Promicron Nanocalc.

#### 8.2 Measurement of layer thickness and refraction index with spectral ellipsometry

Measurement of thin metallic layers or thin layers made of silicon oxide, silicon nitride, poly silicon or photo resists on 150 mm silicon wafers with thicknesses of a few nanometers up to several micrometers; measurements are carried out with a Sentech Senduro Spectroscopic Ellipsometer.

#### 8.3 Measurement of height profiles

Measurement of wafer bend and the height differential on 100 mm, 150 mm and 200 mm wafers as well as on various sized samples up to a 200 mm diameter with a tactile profilometer with a vertical resolution of 1 nm and a horizontal resolution of  $\leq 5\mu$ m; measurement is carried out with a Veeco Dektak 8.

#### 8.4 Measurement of precise location

Measurement of precise location on wafers with a maximum of 300 mm diameter and on mask substrates of up to 230 mm edge length with a reproduction capability of 3 nm (3sigma). The measurement is carried out with a KLA-Tencor LMS IPRO II

Contact

Dr. Martin Zimmermann Dr. Jörg Butschke phone: +49 711 21855-423 phone: +49 711 21855-453

# 8.5 Measurement of structures on wafers and mask substrates with scanning electron microscopy

Fully-automatic measurement of structure widths between 50 nm and 10  $\mu$ m with a precision of at least 1 % on 150 mm wafers. Resists and etching structures can be measured, measurement is carried out with a CD-SEM Hitachi S8820-S.

Fully-automatic measurement of structure widths between 20 nm and 5  $\mu$ m with a precision of at least 1 % on 6 inch mask substrates. Resists and etching structures can be measured, measurement is carried out with a CD-SEM Advantest LWM9000.

# 8.6 Characterization of structures on wafers and mask substrates with scanning electron microscopy

Field emission scanning electron microscope (FE-SEM) Zeiss LEO-1560 for the display of samples with a resolution of up to 2 nm depending on measurement conditions and sample, large sample chamber for wafers with a diameter of up to 150 mm.

Field emission scanning electron microscope (FE-SEM) Zeiss Ultra 60 for the display of samples with a resolution of up to 2 nm depending on measurement conditions and sample, large sample chamber for wafers with a diameter of up to 150 mm with additional detectors, such as EsB, AsB and an energy-dispersive x-ray detector (EDX) Bruker XFlash 4010 for testing of their chemical compilation.

## 8.7 Characterization of thin dielectric layers on wafers

Measurement of the minority charge carrier life cycle using  $\mu$ -PCD technology on passivated silicon wafers with a size up to 200 mm to characterize the wafers and the barrier in terms of contamination and defects. Advanced characterization of thin dielectrics as well as their barrier using V-Q measurement technology (flat band stress V<sub>fb</sub>, density interface traps Dit, tunnel field stress E<sub>tunnel</sub>, electrical oxide thickness T<sub>ox</sub>, mobile charging Q<sub>m</sub>).

Measurements are carried out contact-free on unstructured wafers using the WT2000 made by the Semilab company.

## 8.8 Defect measurement (Light Point Defects, LPD) on wafers

Measurement of diffusing defects (Light Point Defects, LPD) with a size of > 0.1  $\mu$ m on 150 mm and 200 mm Si-wafers. Measurements are carried out contact-free on unstructured wafers using the WM-7 made by the Topcon company.

# 8.9 Measurement of structures, height profiles, and surface roughness using atomic force microscopy (AFM)

Characterization of surface topography on arbitrary substrates up to a diameter of 300 mm and up to a thickness of 25 mm (wafer, masks, fragments, chips), both resist and etched structures can be studied, regardless of electrical conductivity. Lateral resolution << 1 nm, but strongly depends on structure geometry. Height differences between < 0.1 nm and 15  $\mu$ m can be measured. Accuracy of the calibration 3%. Side wall profiles can be resolved if their aspect ratio is < 5:1. Samples up to a diameter of 200 mm can be tilted by 20° in order to study even steeper side walls including undercuts (parts of the sample surface may possibly not be reachable). Measurement of surface roughness at a vertical noise level of 0.07 nm (rms). Measurements are carried out using a Park Systems AFM NX20-300.

#### Contact

Dr. Martin Zimmermann Dr. Jörg Butschke phone: +49 711 21855-423 phone: +49 711 21855-453

## 9 Packaging

## 9.1 Wafer thinning

Thinning of 4, 6 and 8 inch silicon wafers on thicknesses of 1000  $\mu$ m up to 200  $\mu$ m (<u>+</u>5 $\mu$ m). It is also possible to thin wafer pieces and individual chips. In addition, thin chips with a thickness up to 20  $\mu$ m can be manufactured. Also, using the Taiko process the equipment is able to create a membrane thickness of 50  $\mu$ m. Deposition is carried out with a type DAG 810 equipment by the Disco company.

## 9.2 Sawing silicon wafers

Sawing silicon wafers for a size up to 200 mm, sawing is carried out with a type 641 wafer saw of the Disco company.

Reduction of wafer size, such as 200 mm down to 150 mm (up to 3 inches). These size-reduced wafers can be continued to be processed in semiconductor equipment without a problem. Sawing is carried out with a type 641 wafer saw by the Disco company.

## 9.3 Removing dies from foil

Automated picking of dies off foil and sorting them in waffle packs with the help of automated image recognition, picking is carried out by a FAB<sup>1</sup> die bonder of the Amadyne company.

## 9.4 Die bonding

The bonding of the dies is ordinarily carried out using a time/pressure dispenser. There is a possibility, however, to set glue using tiny glue points with a Liquidyn-Jet system. Standard ceramics packages, plates and foil are available. Bonding is carried out with the FAB<sup>1</sup> die bonder made by the Amadyne company.

## 9.5 Wire bonding

Wire bonding with AlSi (1%) wire at a 25  $\mu$ m diameter, bonding is carried out with a type G5/6400 thin wire wedge bonder made by the F & K Delvotec company. Wire bonding with gold wire at a 25  $\mu$ m diameter, bonding is carried out with a type 6200 gold ball bonder made by the F & K Delvotec company.

## 9.6 Testing of the wire/bonding and soldering connections

Testing of the wire connection tensile strength (wire pull test) using a Pull-testers Dage Series 4000 with a calibrated 200 g measurement load cell.

Testing of the die shear force (the shear test) and/or the lid shear force (lid shear test) using the Pull-testers Dage Series 4000 with a calibrated 10 kg measurement load cell.

## 9.7 Baking oven

Baking of the glue after die-bonding under protective gas (N<sub>2</sub>) up to 300 °C, baking is carried out in UNE400 oven made by the Memmert company.

Dehumidifying of the packages prior to sealing using inert gas  $(N_2)$  and vacuum, dehumidifying is carried out with a VO 200 vacuum oven made by the Memmert company. (Minimal pressure: 10 m torr and maximum temperature: 200 °C).

#### Contact

Dr. Martin Zimmermann Dr. Jörg Butschke phone: +49 711 21855-423 phone: +49 711 21855-453

### 9.8 Package seal

Solder seal in pure hydrogen atmosphere as well as all possible N<sub>2</sub>/H<sub>2</sub> ratios under vacuum with up to 400  $^{\circ}$ C (relevant hordes are included). Sealing is carried out in a VL20 vacuum oven made by the Centrotherm company.

## 9.9 Packaging or solder cleaning

Activation of surfaces (solders) with a microwave plasma with an Ar/H<sub>2</sub> mix (60/40) will result in better solder connections. Activation is carried out in a VL20 vacuum oven made by the Centrotherm company.

## 9.10 Testing the impermeability of the packages

Testing for coarse and fine leakages using a bubble tester and a helium leakage tester.

### 9.11 Package printing

Printing on packages using a type PAD tampon printer made by the Massek company. The stereotypes are manufactured at the IMS.

Contact

Dr. Martin Zimmermann Dr. Jörg Butschke phone: +49 711 21855-423 phone: +49 711 21855-453

Institut für Mikroelektronik Stuttgart Foundation under civil law

### **IMS CHIPS**

Allmandring 30a 70569 Stuttgart

Phone+49 711 21855-0 Fax +49 711 21855-111 Email info@ims-chips.de

http://www.ims-chips.de